# Wireless RF Design Challenges

Ken Hansen

Motorola, Inc., Austin, Texas, 78729, U.S.

**Abstract** — The challenges and opportunities for the RF designer have perhaps never been greater. The drive to higher levels of integration in the extremely competitive cellular chipset market place; the emergence of new wireless communications links such as Bluetooth and WLAN; and the continual need to provide multi-band, multi-mode, multi-service, modulation independent, cost effective transceivers have all produced a great demand for RF design skills. This paper will discuss the markets, system level specifications, and RF design challenges.

## I. INTRODUCTION

During the 90's, the tremendous growth of the cellular phone industry fueled the development of RF semiconductor design and components both for infrastructure and subscriber equipment. However, over the last three years the cellular market growth rate has dramatically decreased with the total TAM during this period remaining roughly flat at approximately 400 million units. Nonetheless, the wireless communications market segment represents the single largest market segment for semiconductor manufacturers. During this time, the cellular phone industry has moved beyond 2G with introductions of GPRS, CDMA 2000 1X, and 3G. Wireless products now more than ever are being differentiated by additional services and features. Phone manufacturers have either begun shipping or will shortly ship phones with one or more additional services chosen from GPS, Bluetooth, or WLAN. Additionally, new wireless devices feature color displays and cameras that create the beginning of a technology opportunity for the delivery of video.

Market adoption will be driven by the ability of semiconductor manufacturers to produce flexible, cost-effective, and power efficient multi-band, multi-mode, multi-service, modulation independent solutions to address the evolving market needs. Providing the enhanced capability that enables additional features demands higher levels of integration and places new challenges on the RF designer.

## II. MARKET TRENDS

It has been estimated that the total number of wireless subscribers today is approximately 1 billion and that by

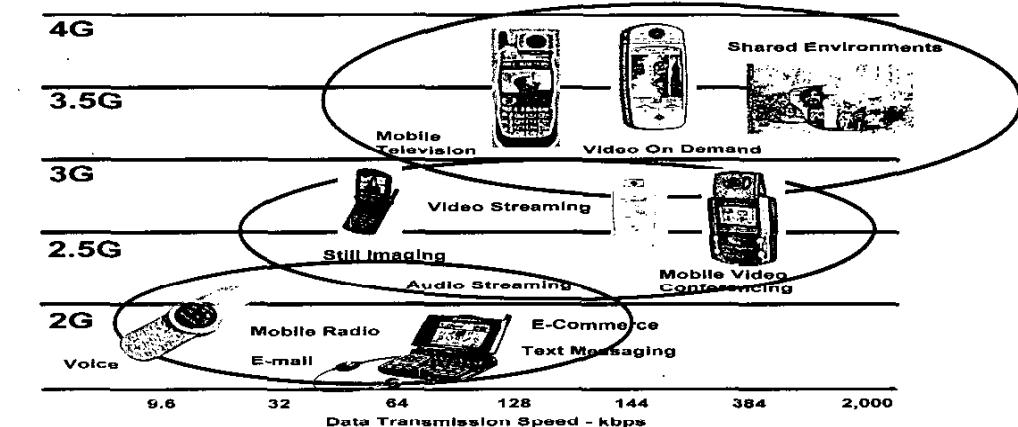

the year 2005 the number of mobile subscribers will exceed the number of fixed subscribers. Additionally, the number of mobile internet subscribers has grown from essentially no use in 2000 to an expectation of over 200,000 users in 2003 and roughly 1 billion users by the end of the decade. [1] While the primary benefit of wireless communication today remains voice communications that provide the ability to communicate anytime, anywhere, it is clear that a significant additional benefit of untethered data communications is beginning to emerge. Figure 1 shows the capability that will be enabled with increasing data rate provided by enhancements to 2G, the introduction of 3G, and future digital cellular generations.

There has been and will continue to be a convergence of wireless communication technologies and devices into the same subscriber unit. For example, UMTS operates in multiple RF bands (900MHz, 1.8GHz, and 1.9GHz), with different access schemes (GSM and WCDMA), different modulation (GMSK and QPSK), and different bandwidths (200KHz and 5MHz). GSM has migrated to GPRS and shortly the industry will have EDGE capable phones. The market has seen the convergence of a PDA and a cell phone device into a single unit. With the introduction of short message service into the cell phone, the pager function has been combined into the phone. New communication systems have been developed (Bluetooth, WLAN) and are being incorporated into the phone to provide local connectivity. Both are characterized by utilizing unlicensed spectrum, operating over short ranges (1-100m), providing high data rate throughput (>1Mbps) and are being integrated into a cell phone. In addition, GPS is being included into cell phones to satisfy a) the U.S. accuracy requirement for mobile 911 emergency services or b) a desire for location based services.

Wireless communications have had only a small impact in the office in the form of paging and in the home in the form of cordless phones, garage door openers, and TV remote controllers. Both the home and the office offer potential growth markets for wireless communication devices. For quite some time, there has been a concept of the wireless home. With the introduction of WLAN and the potential of Ultra Wide Band (UWB), the ability to deliver high data rates for video distribution in the home becomes feasible. Similarly the transformation from

circuit switched to packet switched data is enabling VoIP based phones in the office. These phones will eventually become dual mode phones for use at the office utilizing VoIP technology and as the every day cellular phone.

With the addition of color displays and cameras to the phones, video messaging will become a new means of communicating. As the capability to send and receive video grows, there will become a demand for digital video broadcasting to allow for television programs to be viewed on the phone. Similarly the color display will enhance and enable new levels of gaming. It is likely that interactive multiple player gaming will occur on all phones, perhaps set up on a separate license free RF link.

Many new ways of leveraging short range wireless communications will develop as low cost wireless modems become available. For example, each year new toys that can communicate with each other appear on the market. Car keys will eventually be equipped with transponders to allow the user to locate them quickly when they've been misplaced. These and other examples of machine to machine communications are areas for market growth.

### III. TRANSCEIVER DESIGN CONSIDERATIONS

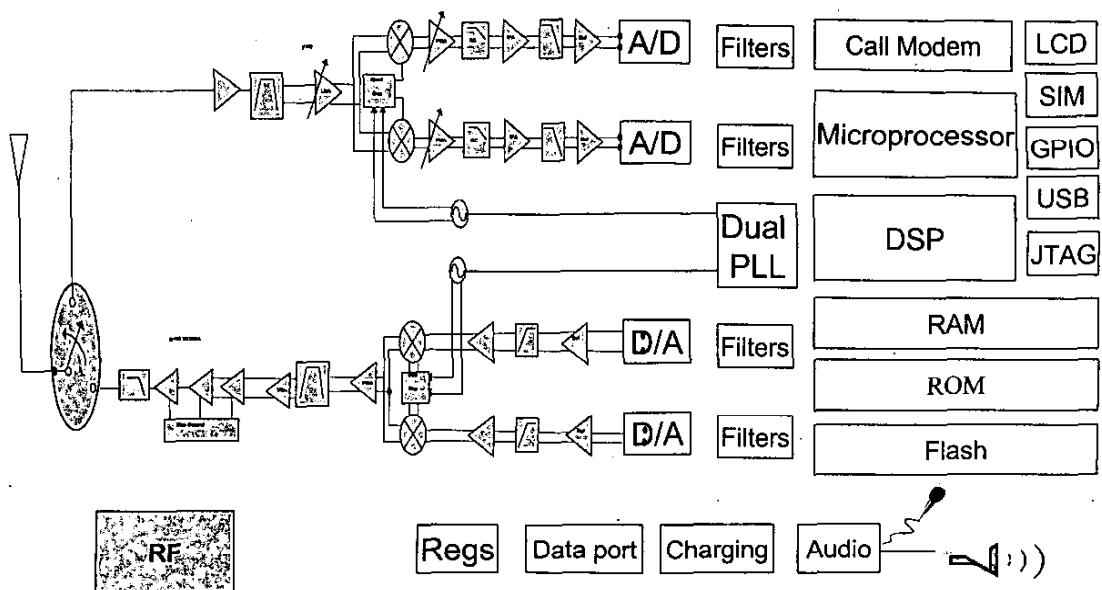

The primary goal of the semiconductor designer is to provide the cellular phone manufacturer with a solution that optimizes cost, current drain, part count, size, and new phone development cycle time. RF designers can increase the design value by either: 1) increasing range by improving receiver sensitivity; 2) improving interference performance; or 3) providing increased talk time. To some extent improvements in one of these three areas can be traded off for an improvement in another area. Shown in Figure 2 is a typical digital phone block diagram. Those blocks that are highlighted indicate elements that are typically considered for integration onto an RFIC or module. Shown in Fig. 3 is a variety of different wireless communications systems which demonstrates the dramatic specification differences.

### IV. RF INTEGRATION

Integration can be achieved at the silicon or module level. To the phone manufacturer, either one is seen as a size and part count reduction with the expectation of a price reduction. To date, higher levels of integration have been achieved on the receiver in silicon and on the transmitter with modules. To achieve the highest level of system integration, RF and analog circuits must be combined with digital circuits on CMOS. It is generally accepted that the PA is not a candidate for high level

integration due to technology limitations that would reduce power added efficiency and the inability to remove the thermal dissipation effectively. The primary technology limitation to achieving a single chip solution is isolation. Despite this technical challenge, single chip Bluetooth ICs with 0dBm output power are commercially available. It has been shown for a GSM phone that a highly integrated small signal RFIC can be built that includes an on board TX VCO that meets the very difficult specifications of

$-162\text{dBc}/\sqrt{\text{Hz}}$  at 10 MHz away from the carrier. [2] Work also began as early as 1995 [3] on CMOS receiver designs. However, the specifications for a GSM phone, including the need for external high speed memory, have been too difficult to achieve on a single chip due to the isolation issues. WLAN adds one other technical challenge which is frequency of operation. For 802.11a the receive and transmit signals are in the 5-6 GHz range. However, the  $f_c$  and  $f_{\text{max}}$  of a  $0.13\mu$  bulk CMOS process will be adequate to meet the operating frequency requirement.

There are other factors to be considered in the development of a single chip CMOS solution. As the industry moves to 90nm technology, the increasing cost of a mask set will demand a greater first pass success rate. RF and analog designs have historically required multiple passes to complete the IC. Thus it will become imperative to substantially improve the modeling and simulation tools and/or design tunable and programmable elements to provide initial design optimization and eventual yield optimization in production. [4]

Related closely to the complexity of RF design is the challenge of moving the design from one technology node to the next for cost reduction and performance improvements. For digital designers, the process is well known. However, for RF and analog design, the design typically does not shrink more than 10-20% which would not be cost effective. Additionally, there is the challenge of how to move the design quickly, particularly when it is likely that the supply voltage is simultaneously lowered. Tools are being developed but are in their infancy that would provide the designer with the ability to optimize a design based upon a topology starting point. This type of tool would be an enabler for migrating RF and analog circuits if sufficient supply voltage is available.

Another key challenge to integration is the maximum voltage the technology node can handle. For RF/analog circuits, dynamic range is proportional to the signal to noise ratio. Signal level is roughly proportional to the maximum voltage. Thus a 20% reduction in supply voltage is at least a 1.6dB reduction in dynamic range. Either improvements in the noise level of the design, a

better circuit topology, or a thicker oxide device to support higher voltage must be provided to achieve higher dynamic range circuits.

One motivation for integration can be current drain reduction. This would largely be realized by the elimination of power used to drive the bond pad, bond wire, and PC board loads. For digital circuits, power drain is reduced as supply voltage is decreased which typically occurs when moving from one technology node to the next. However, for RF/analog circuits this generally is not true. In particular for constant power circuits where the losses are ohmic ( $I^2R$ ), it is rather preferred to increase the voltage and thus minimize the loss achieving the best power consumption. Integration of RF circuits onto baseband chips presents a number of challenges and trade offs the RF design must make.

## V. RF CIRCUITS

The traditional challenge of designing a receive lineup by balancing noise figure, intermodulation, and power gain per stage still exists. The area of design that is often overlooked is the RF front end consisting of the antenna through the RF filters (typically SAWs) shown in Figure 2. Key design parameters for the antenna is 15-20% fractional bandwidth while maintaining a high efficiency, for the RF switch greater than 30dB isolation and less than 0.6dB insertion loss, and for the RF filter a stop band rejection of greater than 40dB. In addition, SAW filters are one of the larger discrete elements of a phone and an internal antenna is preferred for esthetics, mechanical robustness, and size. The challenge is to develop a low cost, miniaturized antenna capable of meeting the performance requirements and to eliminate the RF switch and SAW filters. If these elements are treated as a system rather than stand alone parts, can this goal be achieved.

Another RF circuit that is particularly challenging is the VCO. Recently, the LC tank circuit of the VCO has been integrated. The limitation in the past has been the ability to integrate the inductor with a reasonable Q (20@1GHz). To achieve high Q, increased process complexity in the form of thick metallization and a high resistivity substrate or use of bond wires and a circuit approach that can tolerate the large variability in inductor value is required. The disadvantage of both of these approaches is that due to the limitation of realizable Q, component tolerances, and other circuit noise sources a substantial increase in current (3-4X) is required over a discrete LC tank approach. The design challenge is to determine an approach that allows for VCO integration but brings the current drain more in line with the discrete LC tank solution.

Design of the transmitter presents several challenges. Although Zero IF systems have been built on the receiver side, the complimentary technique of direct launch on the transmit side has not been commercially developed. However, there is work being done in this area. [5] The direct launch scheme conceptually reduces the number of VCOs required and eliminates the need for external filters thus lending itself to integration. However, technical problems that must be simultaneously resolved are power drain, power control over a wide dynamic range, linearity, and carrier feed through.

A key element in the transmitter lineup is the PA. Transmitter designs must meet splatter, harmonic, and transient ramp up/down requirements while maintaining a high power added efficiency (PAE). A trend in the industry is to move to modules (for example Motorola MMM 6010 power amplifier module) to more tightly control impedance variations that the PA device will see. Furthermore, to the cellular phone manufacturer the module solution becomes a part count and size reduction. Integrated into the module are the PA device, PA bias control, filters, antenna switches, and DC-DC convertors. Modules are moving from an FR4 organic substrate to an LTCC substrate. The LTCC substrate offers the benefit of integration of some passive components into the substrate thus reducing the integration cost. For the RF designer, this presents the challenge of creating the design without the flexibility or quickly changing component values or topology. This is very significant as this will cause a significant change in the way RF large signal design is done.

For the PA itself, there are a variety of approaches to be considered to maintain efficiency as a function of output power, load, or modulation scheme. Some of these ideas include supply modulation, device switching, dynamic load control, and dynamic scaling of sources/emitters.

Linear modulation schemes providing higher data rates are replacing constant envelope modulation schemes with the introduction of EDGE. For a traditional implementation of a linear PA, PAE suffers due to its operation falling outside the saturated power amplifier mode. The reduction in PAE results in lower battery life. To combat this efficiency loss, polar modulation schemes have been proposed. In this approach, the amplitude and phase are separated, processed through separate paths, and recombined in a manner to allow the PA to always operate at near saturated power level. The phase path is implemented in one of many well known modulation methods. The amplitude is used to modulate the supply of the PA maintaining saturated PA performance. The primary design challenge presented by the polar approach is that the recombination of the amplitude and phase must

be synchronized in time at the modulation frequency rate while passing through different paths prior to recombining. To satisfy the modulation tracking requirement a DC-DC switcher must be built that has a much greater bandwidth than the modulation bandwidth.

## VI. RF DESIGN ENVIRONMENT AND TOOLS

Designing RF circuits is challenging due to the high frequency of operation and the dynamic range of operation. Thus, these circuits are noticeably sensitive to a wide range of parameters including IC layout effects, parasitic resistive, inductor and capacitive effects, substrate effects, distributed versus lumped effects, packaging effects, and board effects. Unfortunately, there is no one tool that satisfies all the simulation needs. For example, a typical tool will usually operate in either the frequency or the time domain but not both. The RF designers today are left with the challenge of dealing with these unknowns as best as they can. There is clearly a need for an integrated design environment that supports a set of tools to handle the parametric effects mentioned above and to provide both frequency and time domain analysis capability.

As protocols become increasingly complex, RF designers will be required to model, simulate, and optimize at the system level. An example might be to determine the EVM of a linear transmitter that is biased, modulated, and compensated under closed loop control of a baseband processor. One of the biggest challenges for the RF designer is understanding somewhat unrelated disciplines like circuit design, microwave theory, analog design, IC layout, CAD tools, and digital

communications, and applying them to an optimal solution.

## V. CONCLUSION

Market dynamics continue to drive new wireless solutions. While cellular phone growth has flattened, substantial growth is expected over the decade and new wireless communications are being introduced. Between new services like 3G or WLAN, convergence of wireless technologies like cellular phones and Bluetooth, new capabilities like digital video broadcasting, or higher levels of integration, there are many challenges and opportunities for RF designers.

## REFERENCES

- [1] UMTS Forum, "The UMTS Third Generation Market- Structuring the Service Revenue Opportunities", 9/02

- [2] S. Dow, B. Ballweber, L. Chou, D. Eickbusch, J. Irwin, G. Kurtzman, P. Manapragada, D. Moeller, J. Paramesh, G. Black, R. Wollscheid, K. Johnson, "A Dual-Band Direct Conversion/ULTF Transceiver for 850 GSM/GSM/DCS/PCS", *ISSCC Digest of Technical Papers*, pp. 230-231, 2002

- [3] J. Crola and M. Steyart, "A single-chip 900MHz CMOS receiver front-end with high performance low-IF topology", *IEEE, J. of Solid State Circuits*, Vol. 30, pp. 1483-1492, December 1995

- [4] Y. Xu, C. Boone, L. Pileggi, "Configurable Analog/RF Integrated Circuits Based on a SiGe Dots Implementation Platform, *Carnegie Mellon University Center for Silicon System Implementation Technical Report Series*, CSSI 03-03, February 2003

- [5] G. Brenna, D. Tschopp, Q. Huang, "Carrier Leakage Suppression in Direct-Conversion WCDMA Transmitters", *ISSCC Digest of Technical Papers*, pp. 270-271, 2003

Fig. 1 Applications made available as a function of data rate provided by next generation cellular systems

Fig. 2 Typical digital radio block diagram with potential RFIC blocks highlighted

|           | Data Rate               | Sensitivity | IP3     | Channel BW | RF Band                     | TX Power | PAE |

|-----------|-------------------------|-------------|---------|------------|-----------------------------|----------|-----|

| GSM       | 10Kbs - 144Kbs - 384Kbs | -102 dBm    | -20 dBm | 200 KHz    | 800, 900 MHz<br>1.8, 1.9GHz | 33dBm    | 60% |

| WCDMA     | 384Kbs - 2Mbs           | -107 dBm    | -5 dBm  | 5MHz       | 1.9GHz                      | 24dbm    | 35% |

| Bluetooth | 1-10 Mbs                | -75 dBm     | -39 dBm | 1 MHz      | 2.4GHz                      | 20dBm    | 45% |

| 802.11    | 10-50 Mbs               | -76dBm      | N/A     | 5MHz       | 2.4GHz<br>5GHz              | 23dBm    | 40% |

| GPS       | 50 bps                  | -136dBm     | N/A     | 2MHz       | 1.5GHz                      | N/A      | N/A |